NEW! RS-232 / I²C-Adapter & Parallel I/O Module

The use and manufacturing of I2C devices is subject to a copyright and patents from philips. This means that if you , as a semiconductor manufacturer or system developer , need to purchase a licence from philips to use I2C technology in your system. As a user: "Purchase of Philips I2C components conveys a license under the Philips I2C patent to use the components in the I2C system, provided the system conforms to the I2C specifications defined by Philips."+

What this seems to mean in practices is that manufacturers called their I2C compatible parts "2 wire interface" chips, that just happen to be compatible with the I2C protocol, rather than pay phillips royalties for the right to actually SAY "I2C"...

Since October 10, 2006, no licensing fees are required to implement the I²C protocol. However, fees are still required to obtain I²C slave addresses allocated by NXP

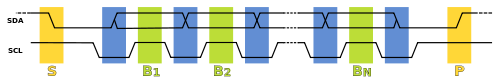

Simple: I2C is very (VERY) simple. I²C uses only two bidirectional open-drain lines, Serial Data Line (SDA) and Serial Clock Line (SCL), pulled up with resistors. The address and the data bytes are sent most significant bit first. The start bit is indicated by a high-to-low transition of SDA with SCL high; the stop bit is indicated by a low-to-high transition of SDA with SCL high. All other transitions of SDA take place with SCL low.

Bidirectional (usually) When the receiving device (called the slave) is not ready to receive another bit of data, it can hold the clock line low, which should be detected by the transmitting device (master) and will prevent further data transfer until the line is released and floats high. This is called "clock stretching".

Multi-Master: A single bus may host multiple master devices. If two devices attempt to transmit on the bus at the same time, the first instance of the data line being held low by only one device will be detected by the other and that device will then stop attempting to transmit. It will then wait for the other device to finish, and then try again. This is called arbitration and ensures there is only one transmitter at a time.

Not power efficient: The requirement for pull up resistors means that I2C is NOT power efficient and so not recommended for use in very low power applications. In some cases, I2C can be used for unidirectional data transmission without pull ups (driving the clock and data high or low). In that mode, there is no feedback from the receiving device; not even when the receiver isn't ready and there can only be one master device. This is really NOT I²C but can be called "2 wire" or synchronous.

Common resistor values: 1k8, 4k7 and 10k are common values, but anything up to 47k (47000 ohms) should work. 1k8 gives good speed performance, 47k (47000 ohms) gives the lowest power use.

DC to 3.4Mbps: Common I²C bus speeds are the 100 kbit/s standard mode and the 10 kbit/s low-speed mode, but arbitrarily low clock frequencies are also allowed. Recent revisions of I²C can host more nodes and run at faster speeds (400 kbit/s Fast mode, 1 Mbit/s Fast mode plus or Fm+, and 3.4 Mbit/s High Speed mode).

Short range: Practical limits on bus length are around 10 feet (a few meters) as the total bus capacitance can not exceed 400pF

ACK After each 8 bit value is sent (address OR data) a single bit ACK is clocked by the master from the slave to the master. For every 8 bits transferred, the device receiving the data sends back an acknowledge bit, as the sending device pulses the clock, so there are actually 9 SCL clock pulses to transfer each 8 bit byte of data. If the receiving device sends back a low ACK bit, by pulling the SDA line low, then it has received the data and is ready to accept another byte. If it sends back a high, by allowing the SDA line to float, then it is indicating it cannot accept any further data and the master should terminate the transfer by sending a stop sequence.

128 to 1K devices (or more): The I²C reference design defines a 7-bit or a 10-bit (depending on the device used) address space. Some devices support additional addressing.

Read/Write: After the address, an additional bit is sent indicating read/write. The result is an 8 bit byte, and a confusing value for the address. For example, to write to device 1 on the bus, you would send a 2 (1<<1+0). That is: The device address, 1, shifted 1 bit to the left (aka doubled) and write (zero) added. To read from the same device, you would send 3 (1<<1+1). That is 1 doubled, plus read (one).

Timing (thanks to Wikipedia)

See also:

See:

Questions:

Comments:

| file: /Techref/i2cs.htm, 9KB, , updated: 2014/5/12 09:06, local time: 2025/6/23 20:32,

216.73.216.97,10-1-151-29:LOG IN

|

| ©2025 These pages are served without commercial sponsorship. (No popup ads, etc...).Bandwidth abuse increases hosting cost forcing sponsorship or shutdown. This server aggressively defends against automated copying for any reason including offline viewing, duplication, etc... Please respect this requirement and DO NOT RIP THIS SITE. Questions? <A HREF="http://sxlist.com/techref/i2cs.htm"> I2C, IIC</A> |

| Did you find what you needed? |

Welcome to sxlist.com!sales, advertizing, & kind contributors just like you! Please don't rip/copy (here's why Copies of the site on CD are available at minimal cost. |

|

The Backwoods Guide to Computer Lingo |

.